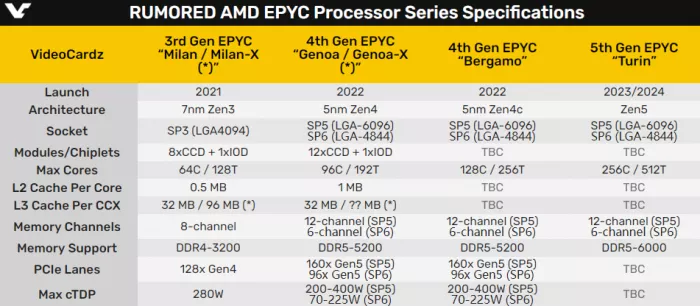

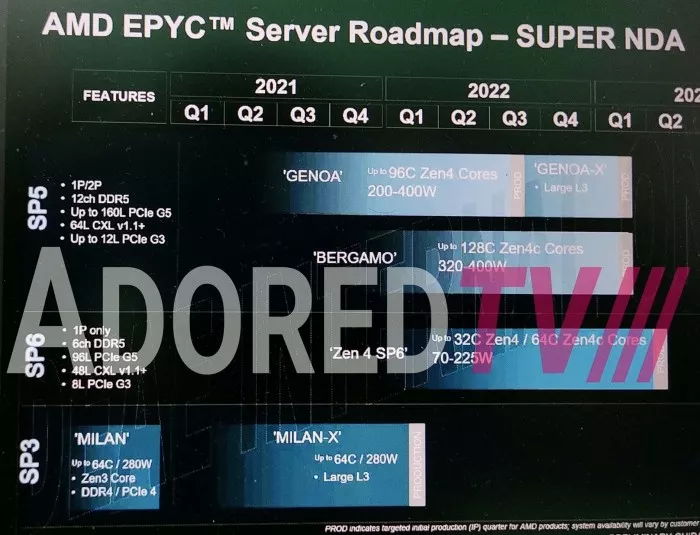

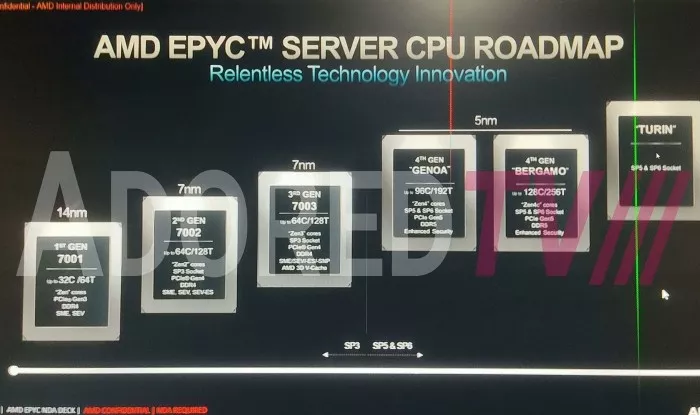

Amd needs to completely change the interface. Starting with zen4 architecture, the Raptor 7000 series on the desktop is changed from AM4 interface to Am5, and the Xiaolong 7004 series on the data center is changed from SP3 interface to SP5 and SP6. The difference is that SP5 series is a high-performance version with complete specifications, while SP6 series only supports single channel configuration for edge computing and telecom infrastructure applications, and the specifications are also streamlined.

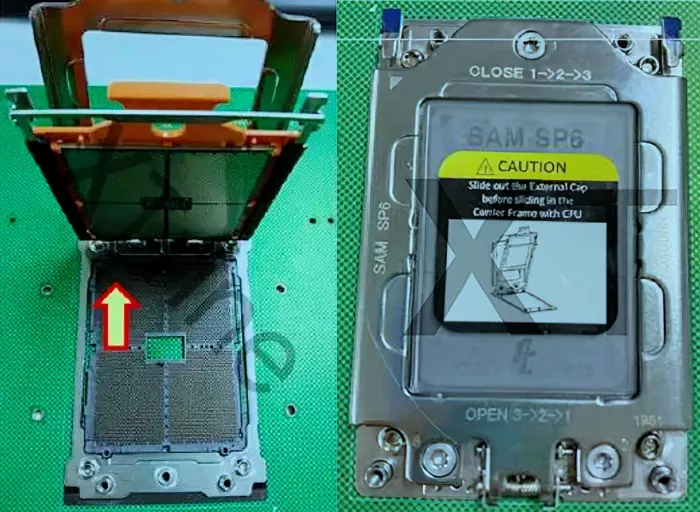

Today, some overseas netizens leaked further details of SP6 interface, including physical drawings and design drawings.

Amd Xiaolong continues the SP3 interface of three generations, also known as lga4094, that is, 4094 contacts, with a length and width of 75.4 × 58.5mm**

SP5 interface, also known as lga6096, naturally has 6096 contacts, which has increased by almost half, and the length and width have also increased to 80.0 × 76.0 mm , with an area increase of nearly 38%.

The alias of SP6 interface is lga4844, with a total of 4844 contacts, which is more than 20% less than SP5, but about 18% more than SP3, while the length and width dimension is maintained at 75.4 × 58.5mm

Of course, SP3, SP5 and SP6 are incompatible with each other.

It is speculated that zen4 Genoa and zen4c Bergamo of SP5 interface will be named Xiaolong 7004 series, and Z of SP6 interface will be named Xiaolong 5004 series to distinguish

The exposure shows that the Genoa series of SP5 interface has up to 96 zen4 cores and 192 threads, and the power consumption range is 200-400W, while the Bergamo series has up to 128 zen4c cores and 256 threads, and the power consumption range is 320-400w**

They all support single and dual configurations, 12 channels of ddr5 memory, 160 PCIe 5.0 buses, 12 PCIe 3.0 buses and 64 CXL v1 1 + high speed interconnect bus.

Genoa also has a derivative version of "genoa-x", which is similar to the current milan-x and also adds 3D v-cache stack cache.

The SP6 interface version has up to 32 zen4 cores or 64 zen4c cores, and the power consumption range is reduced to 70-225w

At the same time, it is reduced to 6-channel ddr5, 96 PCIe 5.0, 8 PCIe 3.0 and 48 CXL 1.1 +, that is, one-third to half of the specifications are cut.

The product code of zen5 architecture is "Turin". There are also two interface versions of SP5 and SP6, but the specific specifications are not clear for the time being. It is expected that there will be up to 256 core 512 threads and 12 channel ddr5-6000.