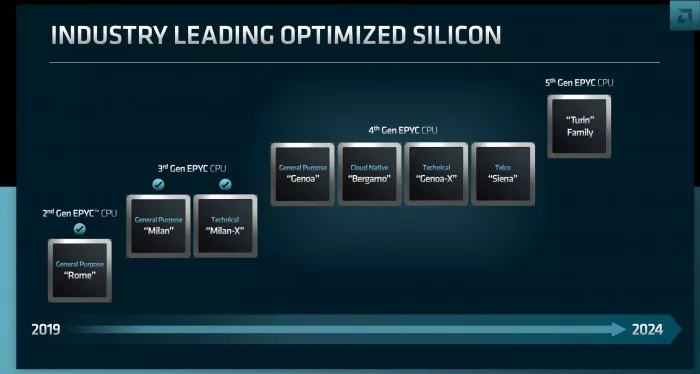

At the same time of publishing the Zen CPU architecture roadmap, amd also showed the roadmap of epyc Xiaolong data center, which is basically synchronized with the architecture, and the products are becoming more and more abundant. In the zen1 and zen2 era, Xiaolong 7001 series and Xiaolong 7002 series have only one product line, which can be used in various scenarios.

In the zen3 era, in addition to the general-purpose Milan, the Xiaolong 7003 series also added milan-x, adding 3D v-cache cache to the stack, which is optimized for computing and database.

In zen4 era, Xiaolong 7004 series will have four different directions:

*"Genoa" (Genoa) *: General Motors, TSMC 5nm, SP5 new interface, up to 96 cores, 192 threads, 12 channel ddr5 memory, PCIe 5.0 bus, support for CXL high-speed bus, release in the fourth quarter of 2022.

"Genoa-x" : similar to milan-x, it is also a superimposed 3D v-cache cache, plus the maximum total capacity of L3 cache of 1+gb. It will be released in 2023**

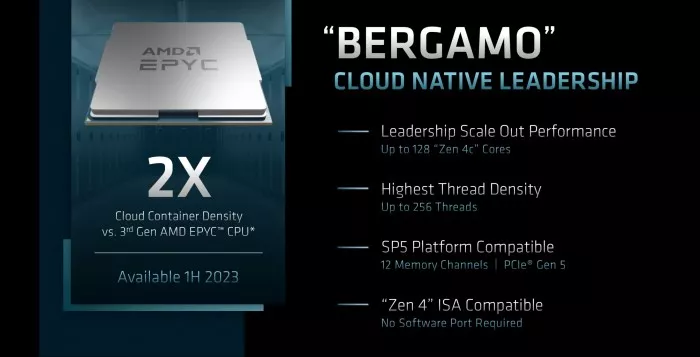

*"Bergamo" *: for cloud storage and computing, the density has doubled. TSMC 4nm, SP5 interface, 128 cores and 256 threads at most, 12 channel ddr5, PCIe 5.0 and CLX may be used. It will be released in the first half of 2023.

"Siena" (Siena) : first released, it is oriented to intelligent edge computing and communication infrastructure, with lower cost. Zen4c architecture, up to 64 cores and 128 threads, specially optimizing the energy efficiency ratio. Issued in 2023**

In the zen5 era, Xiaolong 7005 series has only released a general-purpose product "Turin", which is expected to adopt TSMC 4nm process

From the perspective of the roadmap, zen5 is similar to zen4. There will also be three architecture variants of zen5, zen5 v-cache and zen5c , as well as 3nm process. It is expected that the product line will be at least similar to that in the zen4 era, but more or less.

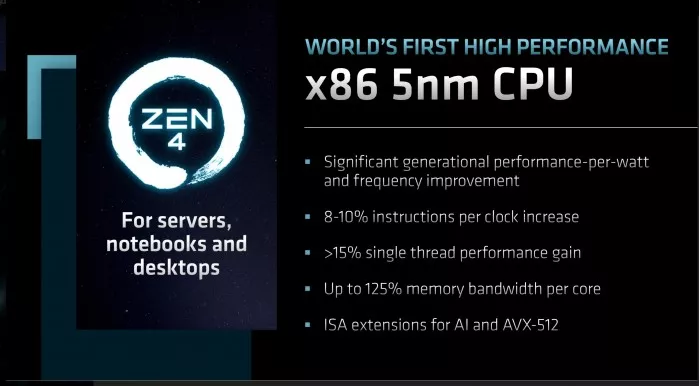

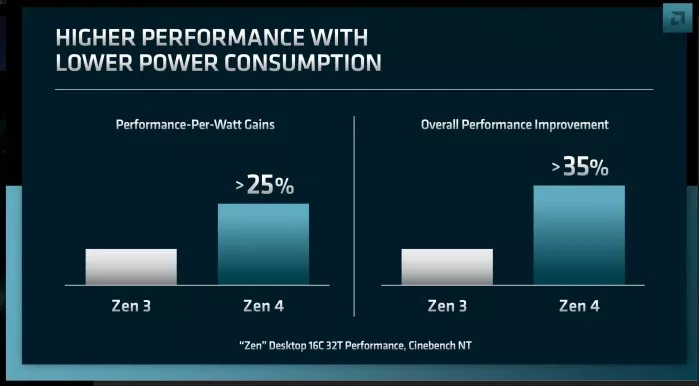

According to AMD, compared with zen3, zen4 is expected to bring 8-10% IPC improvement, more than 15% single core performance improvement, more than 35% multi-core performance improvement, more than 25% energy efficiency improvement, 25% per core memory bandwidth improvement, and add AI and avx-512 instruction sets

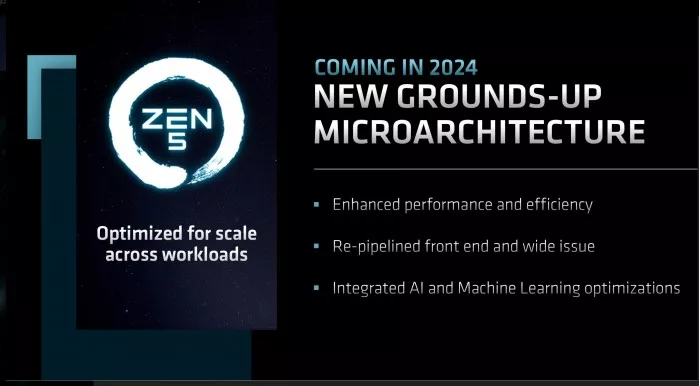

Zen5 architecture will be newly designed, including enhanced performance and energy efficiency, re carding front-end and launch, and integrated AI and ml optimization