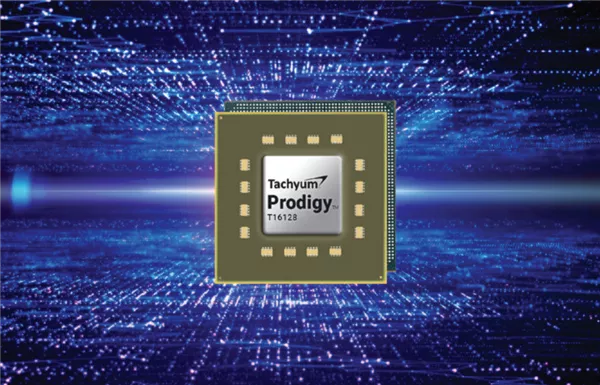

A few days ago, the Silicon Valley startup chip company tachyum announced a magical processor "prodigy", which is known as the world's first "universal processor". It has 128 cores at most, and the frequency is as high as 5.7GHz, which is really incredible. Now, more details Tachyum prodigy processor adopts self-developed architecture, which is the core of 64 bit VLIW ARCHITECTURE and is executed in sequence. However, after optimizing the compiler, it can also be executed in 4-way out of sequence

Each core has another two 1024 bit vector units, a 4096 bit matrix unit, 64KB L1 instruction cache, 64KB L1 data cache, and 1MB L2 cache, and the idle L2 cache can also be used as L3 cache for other cores.

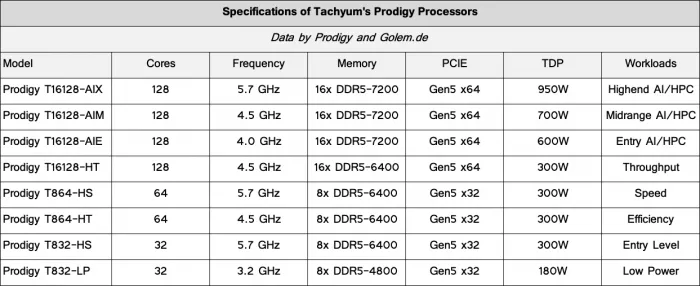

The top-level model "prodigy t16128-aix" has a frequency of up to 5.7GHz, supports 16 channel ddr5-7200 memory, has a maximum capacity of 8tb, also supports 64 PCIe 5.0, and has a power consumption of up to 950W. It must be cooled by liquid cooling

*It is mainly aimed at high-end AI and HPC fields. AI reasoning training performance is 12pflops (120million calculations per second), fp64 HPC computing performance is 90tflops (90trillion calculations per second) * -- AMD risc-v mi250x computing card can run to 96tflops and only needs 560W.

Support two-way and four-way parallel , that is, a single system can achieve up to 512 cores and 32tb memory.

The other three 128 cores , called t16128-aim, t16128-aie and t16128-ht respectively, have frequencies of 4.5ghz, 4.0ghz and 4.5ghz, and power consumption of 700W, 600W and 300w**, of which the memory frequency of HT version is reduced to ddr5-6400.

The 64 core has two types of , t864-hs and t864-ht, with frequencies of 5.7GHz and 4.5ghz , respectively. It supports eight channel ddr5-6400 and 32 PCIe 5.0, and the power consumption is 300w.

*The 32 core also has two , t832-hs and t832-lp, with the frequency of 5.7GHz and 3.2ghz , respectively. The memory frequency of the latter is reduced to ddr5-4800, and the power consumption is 300W and 180W *, respectively.

However, tachyum has not yet had a silicon chip. If everything goes well, it is expected to complete the production in mid August. The TSMC n5p 5nm enhanced version will be used. The core area is estimated to be no more than 500 mm2. The first silicon chip will be obtained in December

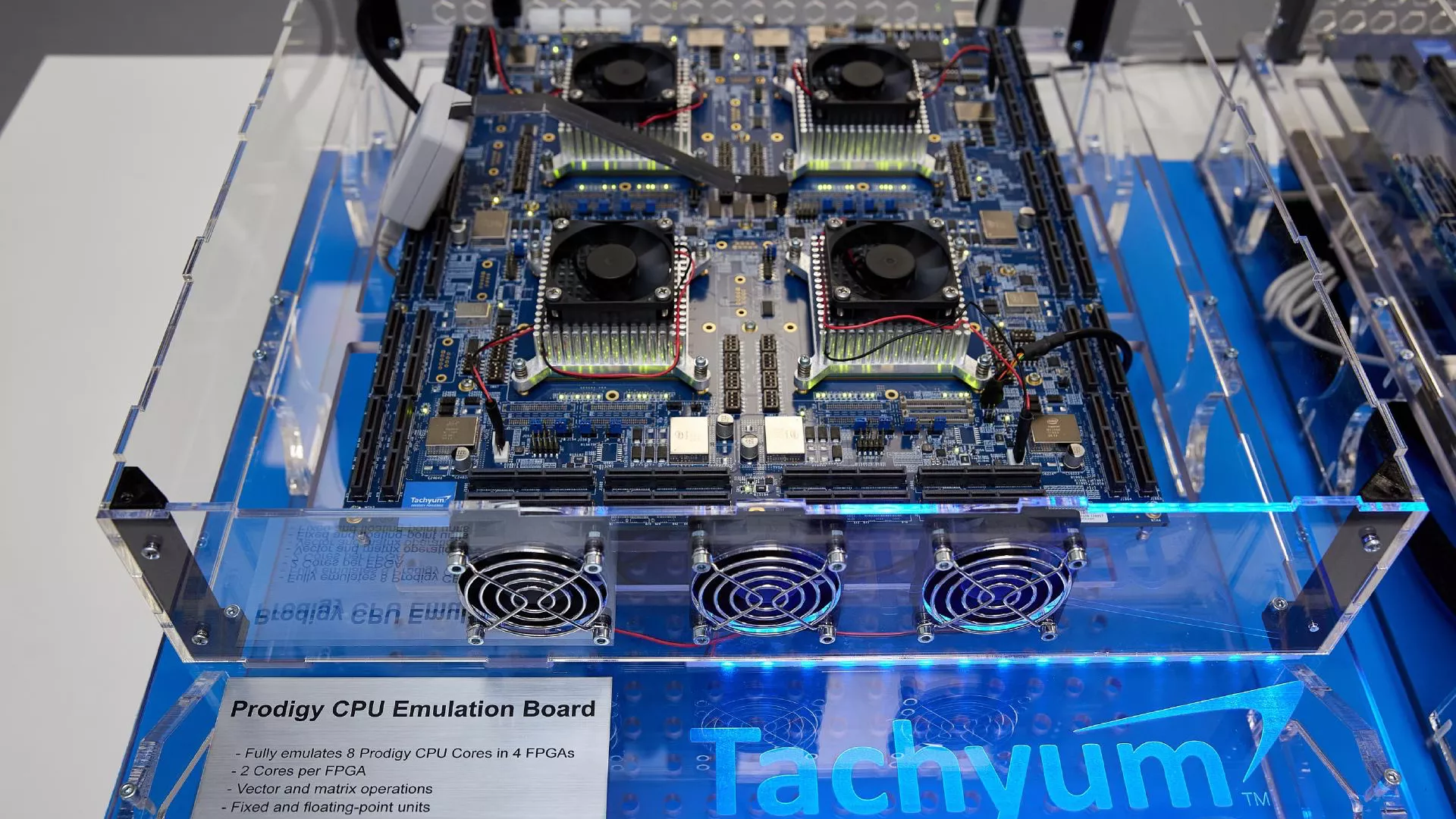

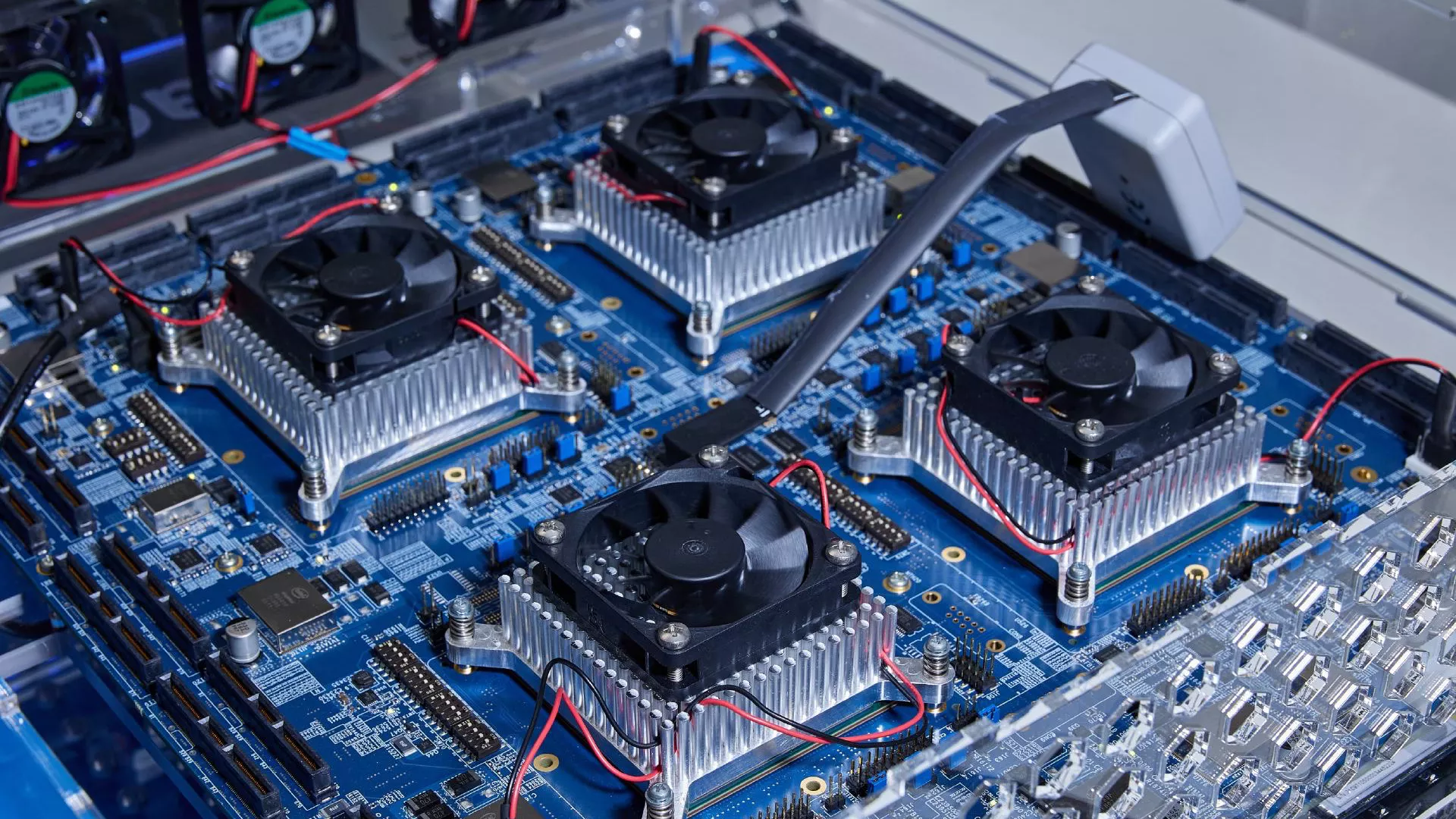

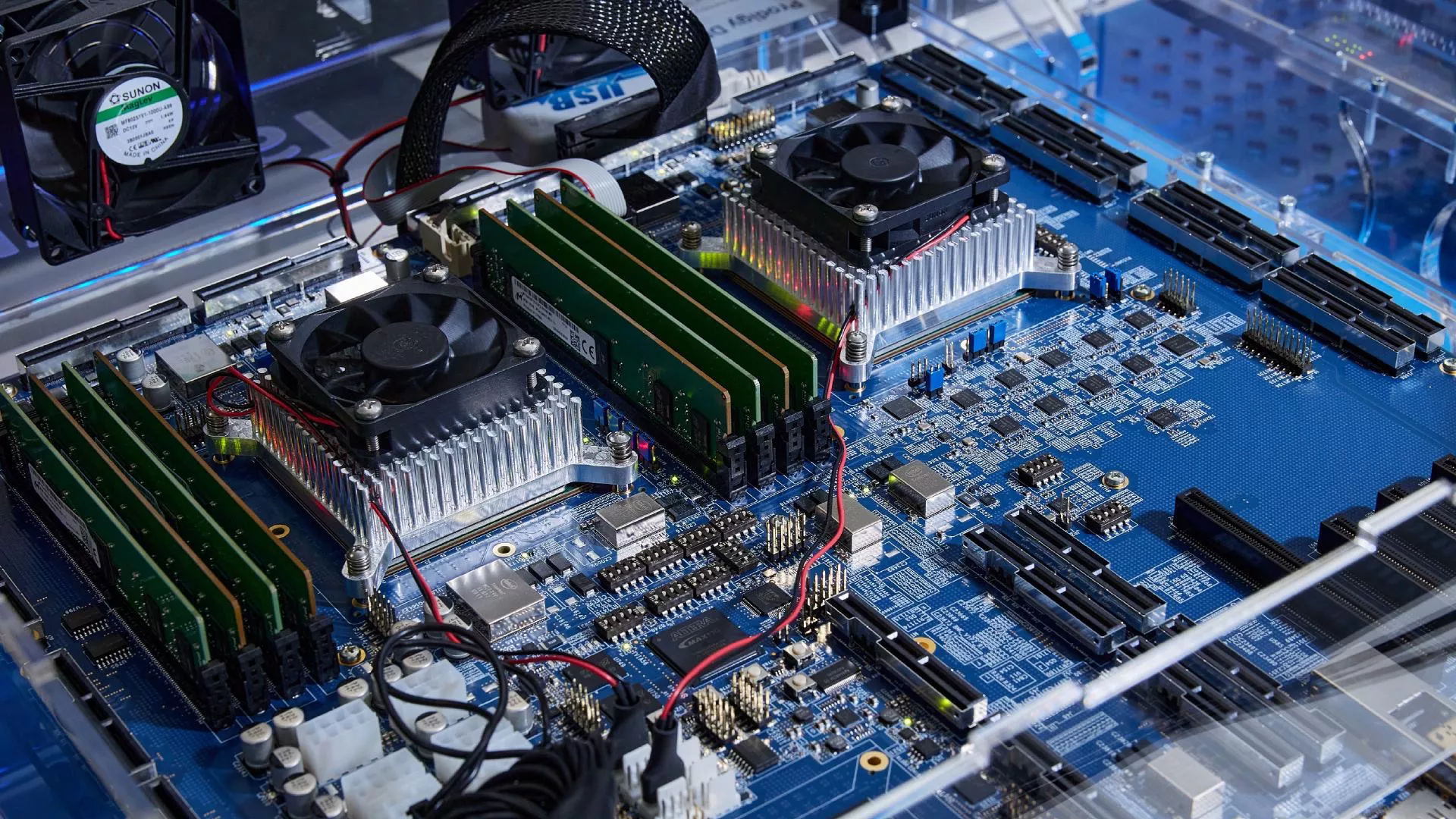

This time, the platform simulated by FPGA, with four simulated eight cores, is displayed on site.

Even though the first generation is still on PPT, tachyum has begun to look forward to the next generation: TSMC N3 3nm, supports PCIe 6.0, and doubles its performance under the same power consumption**